# Third Semester B.E. Degree Examination, Jan./Feb.2021 Analog Electronics

Time: 3 hrs.

Max. Marks: 80

Note: Answer any FIVE full questions, choosing ONE full question from each module.

### Module-1

- 1 a. With necessary equivalent diagram obtain the expression for  $Z_{in}$ ,  $A_{V}$ ,  $Z_{0}$  for Darlington Emitter follower. (10 Marks)

- b. For an Emitter bias circuit (capacitor bypassed), determine  $r_e$ ,  $Z_i$ ,  $Z_O$  and  $A_V$ . Given  $R_B=470~K\Omega$ ,  $R_C=2.2~K\Omega$ ,  $V_{CC}=20~V$ ,  $R_E=0.56~K\Omega$ ,  $C_E=10~\mu F$ ,  $\beta=120$ ,  $r_0=40~K\Omega$ ,  $C_C=10~\mu F$ .

#### OF

- 2 a. Derive the expression for A<sub>V</sub>, A<sub>i</sub>, Z<sub>i</sub> and Z<sub>0</sub> for C<sub>E</sub> fixed bias configuration using complete hybrid equivalent model. (10 Marks)

- b. Consider a single stage CE amplifier with  $R_S = 1$  K and  $R_L = 1.2$  K $\Omega$ . Calculate  $A_i$ ,  $A_i$ ,  $A_i$ , if  $A_i$ ,  $A_i$ ,

## Module-2

- 3 a. Derive the expression for transconductance g<sub>m</sub> for FET. (06 Marks)

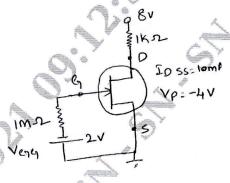

- b. For the circuit shown in the Fig. Q3 (b), calculate (a)  $V_{GS}$  (b)  $I_{DQ}$  (c)  $V_{DSQ}$  (d)  $V_{D}$ .

(10 Marks)

Fig. Q3 (b) **OR**

- 4 a. With necessary equivalent circuit obtain the expression for A<sub>V</sub>, Z<sub>in</sub>, Z<sub>O</sub> for a fixed biased JFET amplifier. (08 Marks)

- b. Derive the expression for Z<sub>i</sub>, Z<sub>0</sub>, A<sub>V</sub> considering common drain amplifier circuit. (08 Marks)

## Module-3

- 5 a. Derive the expression for lower cut-of frequencies due to various RC networks in CE amplifiers. (10 Marks)

- b. Determine the lower cut-off frequency for the emitter follower using BJT amplifier with  $C_S=0.1~\mu F$ ,  $R_S=1~K\Omega$ ,  $R_1=12~K\Omega$ ,  $R_2=4~K\Omega$ ,  $R_E=1.5~K\Omega$ ,  $C_C=0.1~\mu F$ ,  $\beta=100$ ,  $r_0=\infty$ ,  $V_{CC}=15~V$ ,  $V_{BE}=0.7~V$ .

#### OR

Describe Miller effect and derive an equation for Miller input and output capacitance.

(08 Marks)

Calculate the overall lower 3 dB and upper 3 dB frequencies for a 3 stage amplifier having (08 Marks) an individual  $f_1 = 40$  Hz and  $f_2 = 2$  MHz.

Module-4

- Derive the expression for input resistance for a voltage of series and current series feedback. 7 (08 Marks)

- With a neat circuit diagram, explain FET based phase shift oscillator.

(08 Marks)

- With the help of neat circuit diagram. Explain the operation of Colpitts and Hartley 8 oscillator. Write the expression for the frequency of oscillation.

- In a transistor Colpitts oscillator  $C_1 = 1$  nF,  $C_2 = 100$  nF. Find the value of L for a frequency (04 Marks) of 100 kHz.

**Module-5**

- Show that the transformer coupled class A power amplifier has maximum efficiency of 50%. 9

- A single transistor amplifier with transformer coupled load produces harmonic amplitudes in the output as,

$B_0 = 1.5 \text{ mA}$ ,  $B_1 = 120 \text{ mA}$ ,  $B_2 = 10 \text{ mA}$ ,  $B_3 = 4 \text{ mA}$ ,  $B_4 = 2 \text{ mA}$ ,  $B_5 = 1 \text{ mA}$

- Determine the percentage total harmonic distortion.

- Assume a second identical transistor is used along with a suitable transformer to provide push pull operation. Use the above harmonic amplitudes to determine the new (08 Marks) total harmonic distortion.

- Explain with the block diagram, the basic types of voltage regulation circuit. (08 Marks)

- Explain the operation of complementary symmetry class B amplifier.

(08 Marks)